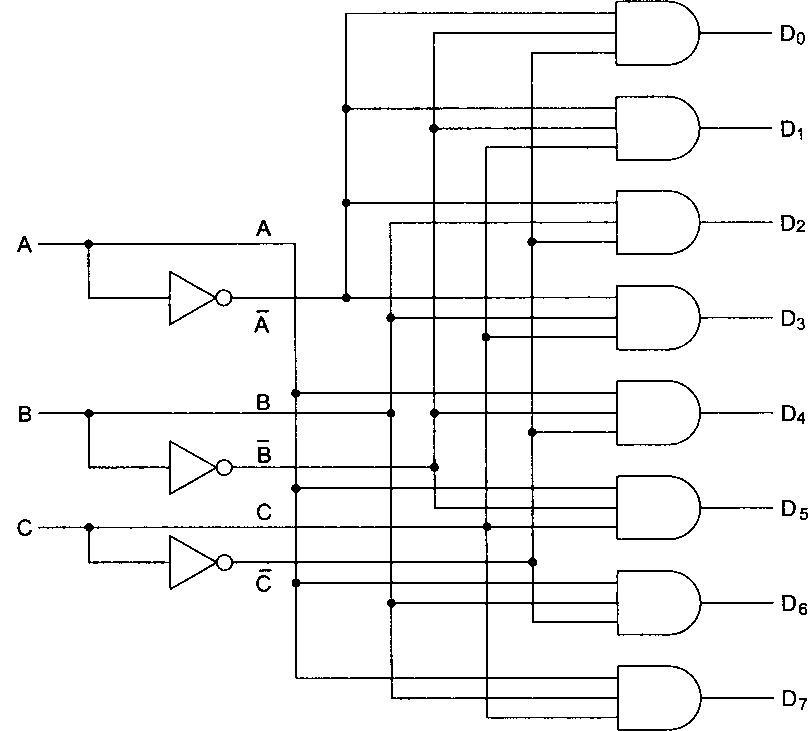

Чтобы понять, зачем нужен декодер, представим себе память, состоящую из 8 микросхем, каждая из которых содержит 1 Мбайт. Микросхема 0 имеет адреса от 0 до 1 Мбайт, микросхема 1 — адреса от 1 Мбайт до 2 Мбайт и т. д. Три старших двоичных разряда адреса используются для выбора одной из восьми микросхем. На рис. 3.12 эти три бита — три входа Л, Б и С. В зависимости от входных сигналов ровно одна из восьми выходных линий (Д), Д) принимает значение 1; остальные линии принимают значение 0. Каждая выходная линия запускает одну

из восьми микросхем памяти. Поскольку только одна линия принимает значение 1, запускается только одна микросхема.

Рис. 3.12. Схема декодера, содержащего 3 входа и 8 выходов

Принцип работы схемы, изображенной на рис. 3.12, не сложен. Каждый вентиль И имеет три входа, из которых первый — это Л или Л, второй — Б или Б, третий — С или С. Каждый вентиль запускается различной комбинацией входов: Д) — сочетанием А В С, Бх — сочетанием Л Б С и т. д.

Компараторы

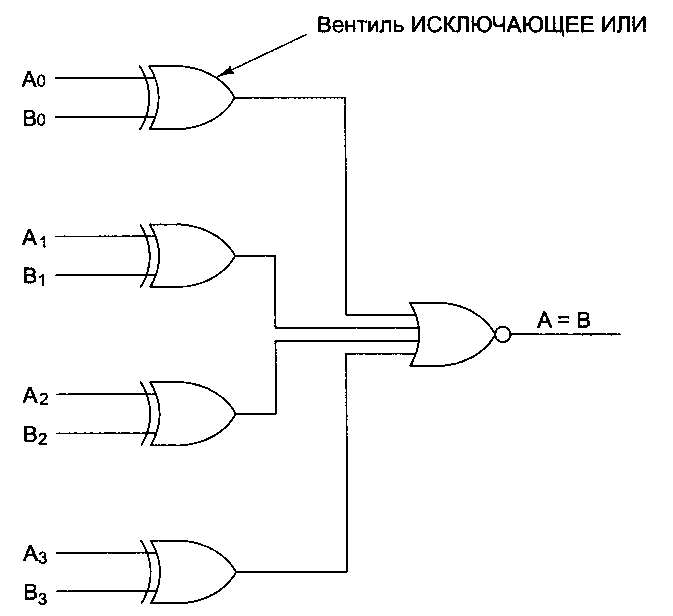

Еще одна полезная схема — компаратор. Компаратор сравнивает два слова, которые поступают на вход. Компаратор, изображенный на рис. 3.13, принимает два входных сигнала, Л и Б, по 4 бита каждый и выдает 1, если они равны, и 0, если они не равны. Схема основывается на вентиле ИСКЛЮЧАЮЩЕЕ ИЛИ, который выдает 0, если сигналы на входе равны, и 1, если сигналы на входе не равны. Если все четыре входных слова равны, все четыре вентиля ИСКЛЮЧАЮЩЕЕ ИЛИ должны выдавать 0. Эти четыре сигнала затем поступают в вентиль ИЛИ. Если в результате получается 0, значит, слова, поступившие на вход, равны; в противном случае они не равны. В нашем примере мы использовали вентиль ИЛИ в качестве конечного, чтобы поменять значение полученного результата: 1 означает равенство, 0 — неравенство.

Рис. 3.13. Простой 4-разрядный компаратор

Программируемые логические матрицы

Ранее отмечалось, что любую функцию (таблицу истинности) можно представить в виде суммы произведений и, следовательно, воплотить в схеме, использовав вентили И и ИЛИ. Для вычисления сумм произведений служит так называемая программируемая логическая матрица (рис. 3.14). Эта микросхема содержит входы для 12 переменных. Дополнительные сигналы (инверсии) генерируются внутри самой микросхемы. В итоге получается всего 24 входных сигнала. Какой именно входной сигнал поступает в тот или иной вентиль И, определяется по матрице размером 24 х 50 бит. Каждая из входных линий к 50 вентилям И содержит плавкую перемычку. При выпуске с завода все 1200 перемычек остаются нетронутыми. Чтобы запрограммировать матрицу, покупатель выжигает выбранные перемычки, прикладывая к схеме высокое напряжение.

Выходная часть схемы состоит из шести вентилей ИЛИ, каждый из которых содержит до 50 входов, что соответствует наличию 50 выходов у вентилей И. Какие из потенциально возможных связей действительно существуют, зависит от того, как была запрограммирована матрица 50 х 6. Микросхема имеет 12 входных выводов, 6 выходных выводов, питание и землю (то есть всего 20 выводов).

Приведем пример использования программируемой логической матрицы. Вернемся к схеме на рис. 3.3, б. Она содержит три входа, четыре вентиля И, один вентиль ИЛИ и три инвертора. Если запрограммировать нашу матрицу определенным образом, она сможет вычислять ту же функцию, используя три из 12 входов, четыре из 50 вентилей И и^эдин из^б вентилей ИЛИ. (Четыре вентиля И должны вычислять произведения ABC, ABC, ABC и ABC) вентиль ИЛИ принимает эти 4 произведения в качестве входных данных.) Можно сделать так, чтобы та же программируемая логическая матрица вычисляла одновременно сумму