Чтобы построить сумматор, например, для двух 16-разрядных слов, нужно 16 раз продублировать схему, изображенную на рис. 3.17, б. Перенос производится в левый соседний бит. Перенос в самый правый бит соединен с 0. Такой сумматор называется сумматором со сквозным переносом. Прибавление 1 к числу 111...111 не осуществится до тех пор, пока перенос не пройдет весь путь от самого правого бита к самому левому. Существуют более быстрые сумматоры, работающие без подобной задержки. Естественно, предпочтение обычно отдается им.

Рис. 3.17. Таблица истинности для полного сумматора (а); схема для полного сумматора (б)

Рассмотрим пример более быстрого сумматора. Разобьем 32-разрядный сумматор на 2 половины: нижнюю 16-разрядную и верхнюю 16-разрядную. Когда начинается сложение, верхний сумматор еще не может приступить к работе, поскольку не знает значение переноса, а узнать его он не сможет, пока не совершится 16 суммирований в нижнем сумматоре.

Однако можно сделать одно преобразование. Вместо одного верхнего сумматора можно получить два верхних сумматора, продублировав соответствующую часть аппаратуры. Тогда схема будет состоять из трех 16-разрядных сумматоров: одного нижнего и двух верхних, £/0 и 11ъ работающих параллельно. В качестве переноса в сумматор £/0 поступает 0, в сумматор 11^ — 1. Оба верхних сумматора начинают работать одновременно с нижним сумматором, но только один из результатов суммирования в двух верхних сумматорах будет правильным. После сложения 16 нижних разрядов становится известно значение переноса в верхний сумматор, и тогда можно определить правильный ответ. При подобном подходе время сложения сокращается в два раза. Такой сумматор называется сумматором с выбором переноса. Можно еще раз разбить каждый 16-разрядный сумматор на два 8-разрядных и т. д.

Арифметико-логические устройства

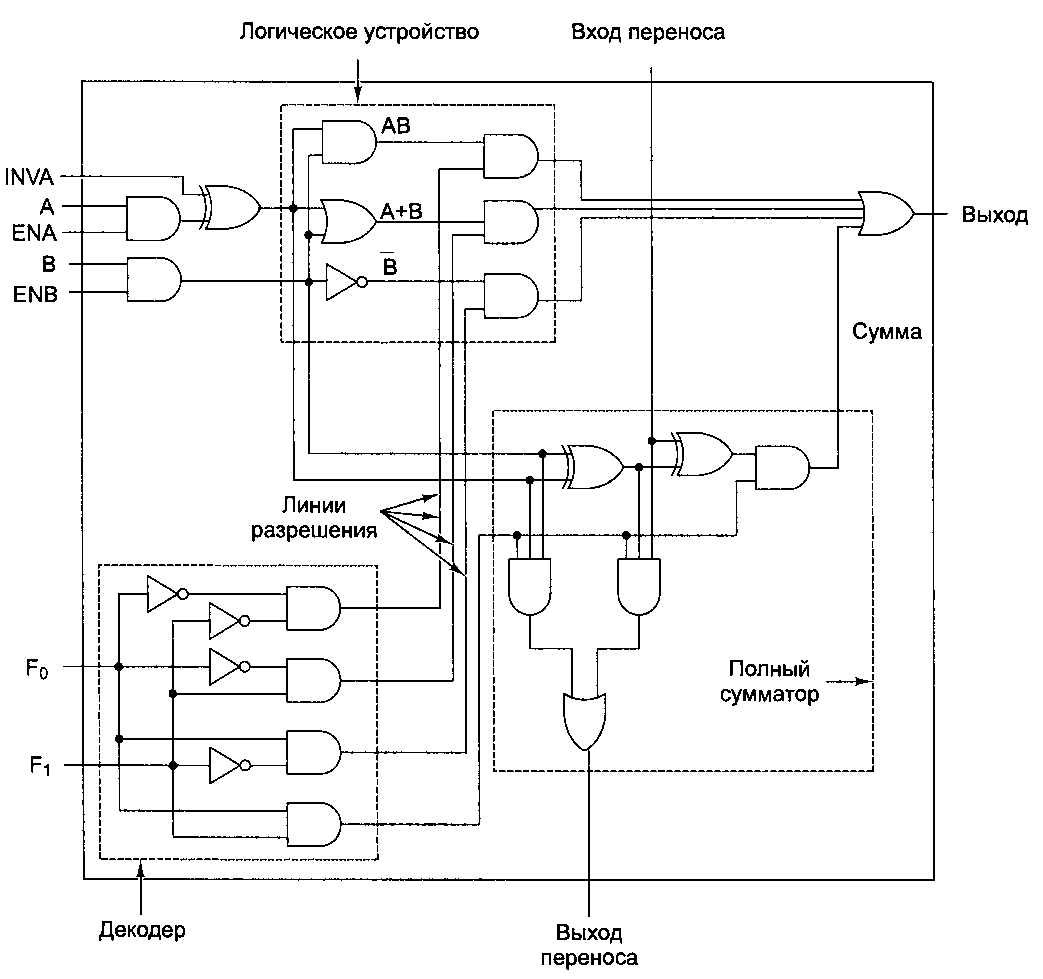

Большинство компьютеров содержат одну схему для выполнения над двумя машинными словами операций И, ИЛИ и сложения. Обычно эта схема для тг-раз-рядных слов состоит из п идентичных схем — по одной для каждой битовой позиции. На рисунке 3.18 изображена такая схема, которая называется арифме тико-логическим устройством (АЛУ). Это устройство может вычислять одну из 4-х следующих функций: Л И В, Л ИЛИ В, В или А + В. Выбор функции зависит от того, какие сигналы поступают на линии Бо и /ч: 00, 01, 10 или 11 (в двоичной системе счисления). Отметим, что здесь А + В означает арифметическую сумму Л и В, а не логическую операцию И.

Рис. 3.18. Одноразрядное АЛУ

В левом нижнем углу схемы находится двухразрядный декодер, который генерирует сигналы включения для четырех операций. Выбор операции определяется сигналами управления ґ0 и і7!. В зависимости от значений ґ0 и выбирается одна из четырех линий разрешения, и тогда выходной сигнал выбранной функции проходит через последний вентиль ИЛИ.

В верхнем левом углу схемы находится логическое устройство для вычисления функций Л И В, Л ИЛИ В и В, но только один из этих результатов проходит через последний вентиль ИЛИ в зависимости от того, какую из линий разрешения выбрал декодер. Так как ровно один из выходных сигналов декодера может