нашего

сайта:

| Статус нашего сайта: |

|

ICQ Information Center |

ICQ SHOP ICQ SHOP5-значные 6-значные 7-значные 8-значные 9-значные Rippers List  ОПЛАТА ОПЛАТА СТАТЬИ СТАТЬИ СЕКРЕТЫ СЕКРЕТЫ HELP CENTER HELP CENTER OWNED LIST OWNED LIST РОЗЫСК!New! РОЗЫСК!New! ICQ РЕЛИЗЫ ICQ РЕЛИЗЫ Протоколы ICQ Протоколы ICQ LOL ;-) LOL ;-) Настройка компьютера Настройка компьютера Аватарки Аватарки Смайлики Смайлики СОФТ СОФТMail Checkers Bruteforces ICQTeam Soft 8thWonder Soft Other Progs ICQ Patches Miranda ICQ  ФорумАрхив! ФорумАрхив! ВАШ АККАУНТ ВАШ АККАУНТ

РекламаНаш канал:irc.icqinfo.ru |

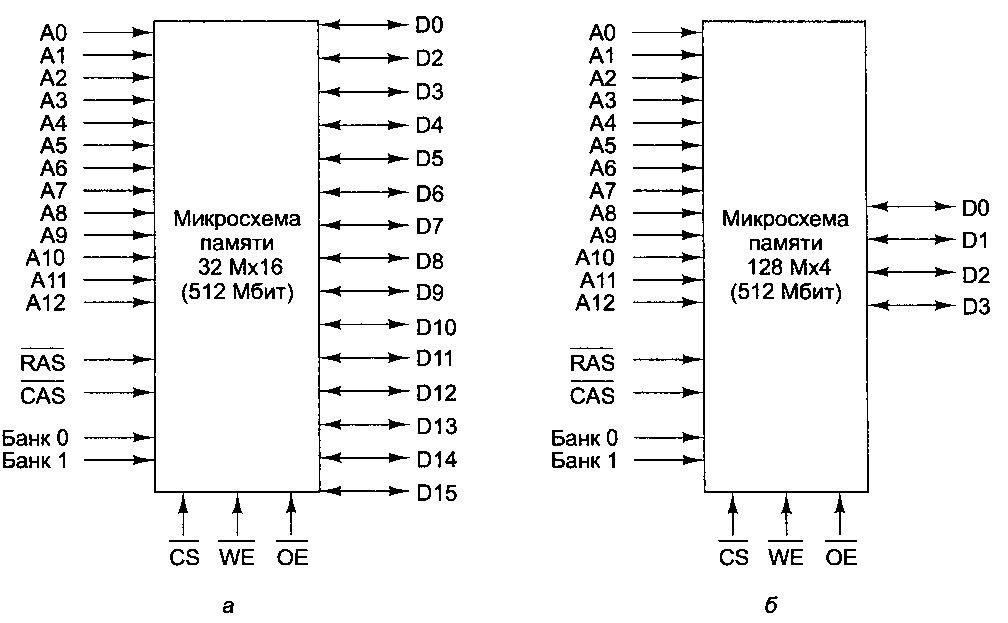

Таненбаум Э.- Архитектура компьютера. стр.139Примеры современных микросхем объемом 512 Мбит показаны на рис. 3.31. В каждой такой микросхеме содержится четыре внутренних банка памяти по 128 Мбит; соответственно, для определения банка требуются две линии выбора банка. На микросхеме 32 M х 16, показанной на рис. 3.31, я, 13 линий выделено для сигналов RAS, 10 — для сигналов CAS и 2 линии — для выбора банка. Взятые в целом, 25 сигналов обеспечивают возможность адресации 225 внутренних 16-разрядных ячеек. На микросхеме 128 M х 4, изображенной на рис. 3.31, б, для сигналов RAS выделено 13 линий, для CAS — 12 линий, для выбора банка — 2 линии. Таким образом, 27 сигналов делают возможной адресацию любой из 227 внутренних 4-разрядных ячеек. Количество строк и столбцов в микросхемах определяется на основании инженерных факторов. Матрица не обязательно должна быть квадратной. Эти примеры наглядно демонстрируют значимость двух не связанных друг с другом проблем в процессе конструирования микросхем памяти. Первая из них касается ширины выхода (в битах) — иначе говоря, количества битов (1, 4, 8, 16 и пр.) в выходном сигнале. Вторая проблема заключается в способе представления битов адреса; здесь есть два варианта: во-первых, биты адресов могут быть представлены одновременно на разных выводах, во-вторых, может быть последовательное представление строк и столбцов — так, как показано на рис. 3.31. Прежде чем приступать к проектированию микросхемы, специалист должен определиться с решением обеих этих проблем.  Рис. 3.31. Два способа организации микросхемы памяти объемом 512 Мбит ОЗУ и ПЗУ Все виды памяти, которые мы рассматривали до сих пор, имеют одно общее свойство: они позволяют и записывать, и считывать информацию. Такая память называется ОЗУ (оперативное запоминающее устройство), или RAM (Random Access Memory — оперативная память). Существует два типа ОЗУ: статическое и динамическое. Статическое ОЗУ (Static RAM, SRAM) конструируется с использованием D-триггеров. Информация в ОЗУ сохраняется на протяжении всего времени, пока к нему подается питание: секунды, минуты, часы и даже дни. Статическое ОЗУ работает очень быстро. Обычно время доступа составляет несколько наносекунд. По этой причине статическое ОЗУ часто используется в качестве кэш-памяти второго уровня. В динамическом ОЗУ (Dynamic RAM, DRAM), напротив, триггеры не используются. Динамическое ОЗУ представляет собой массив ячеек, каждая из которых содержит транзистор и крошечный конденсатор. Конденсаторы могут быть заряженными и разряженными, что позволяет хранить нули и единицы. Поскольку электрический заряд имеет тенденцию исчезать, каждый бит в динамическом ОЗУ должен обновляться (перезаряжаться) каждые несколько миллисекунд, чтобы предотвратить утечку данных. Поскольку об обновлении должна заботиться внешняя логика, динамическое ОЗУ требует более сложного сопряжения, чем статическое, хотя этот недостаток компенсируется большим объемом. Поскольку динамическому ОЗУ нужен только 1 транзистор и 1 конденсатор на бит (статическому ОЗУ требуется в лучшем случае 6 транзисторов на бит), динамическое ОЗУ имеет очень высокую плотность записи (много битов на одну микросхему). По этой причине основная память почти всегда строится на |