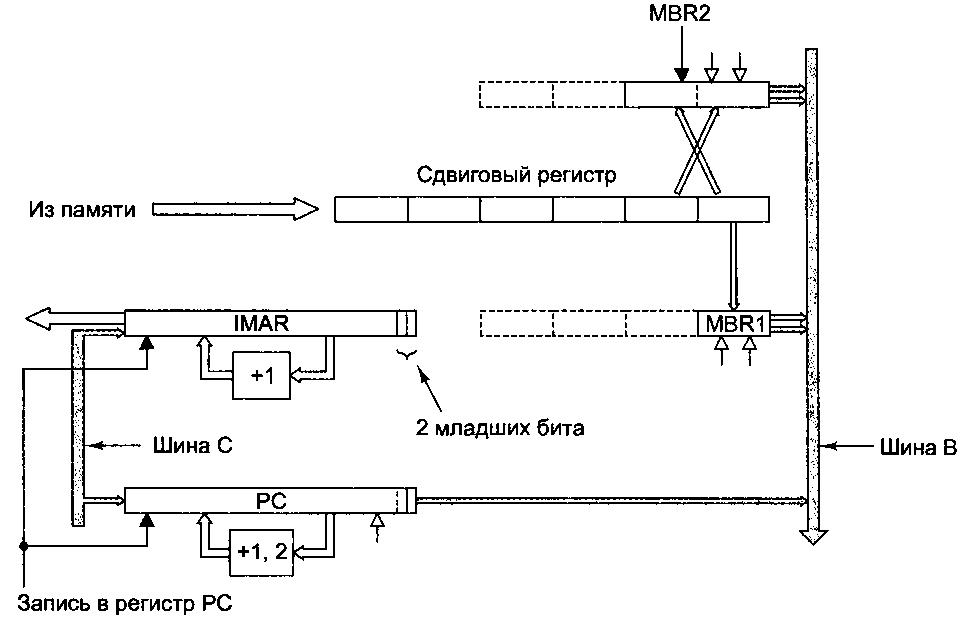

Рис. 4.18. Блок выборки команд в микроархитектуре Mic-1

Всякий раз, когда считывается регистр MBR1, значение сдвигового регистра сдвигается вправо на 1 байт. Всякий раз, когда считывается регистр MBR2, значение сдвигового регистра сдвигается вправо на 2 байта. Затем в регистры MBR1 и MBR2 загружаются самый старший байт и пара самых старших байтов соответственно. Если к этому моменту в сдвиговом регистре остается достаточно места для целого слова, блок выборки команд начинает цикл обращения к памяти, чтобы считать следующее слово. Мы предполагаем, что когда считывается любой из регистров MBR, он заполняется к началу следующего цикла, поэтому новое значение можно считывать уже в последующих циклах.

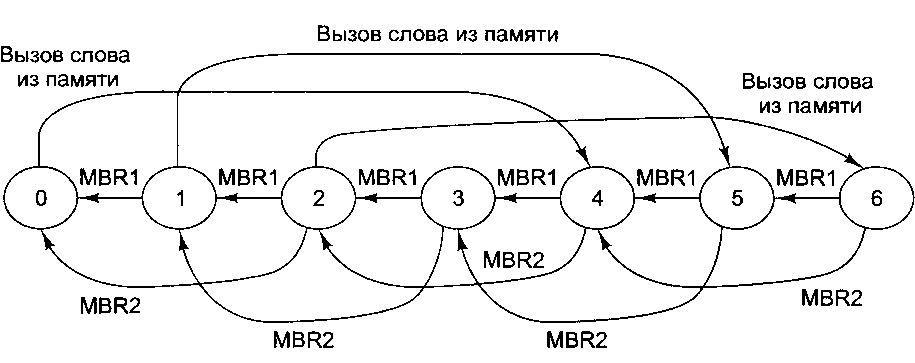

Блок выборки команд может быть смоделирован в виде конечного автомата (Finite State Machine, FSM), как показано на рис. 4.19. Любой конечный автомат характеризуется состояниями (на рисунке это кружочки) и переходами (это дуги от одного состояния к другому). Каждое состояние — это одна из возможных ситуаций, в которой может находиться конечный автомат. Данный конечный автомат имеет семь состояний, которые соответствуют семи состояниям сдвигового регистра, показанного на рис. 4.18. Эти семь состояний соответствуют количеству байтов, которые находятся в данный момент в регистре (от 0 до 6 включительно). Вызов слова из памяти означает считывание слова из памяти и помещение 4 байт в сдвиговый регистр. Переход MBR1 происходит, когда выполняется чтение регистра MBR1, а переход MBR2 — когда выполняется чтение регистра MBR2.

Каждая дуга отражает возможное событие. В нашем конечном автомате возможны три различных события. Первое — чтение одного байта из регистра MBR1. Оно активизирует сдвиговый регистр, самый правый байт в нем исчезает, и осуществляется переход в другое состояние (меньшее на 1). Второе событие — чтение

2 байт из регистра МВИ2. При этом осуществляется переход в состояние, меньшее на 2 (например, из состояния 2 в состояние 0 или из состояния 5 в состояние 3). Оба этих перехода вызывают перезагрузку регистров МВШ и МВ112. Когда конечный автомат переходит в состояния 0, 1 или 2, инициируется обращение к памяти, чтобы вызвать новое слово (предполагается, что память уже не занята считыванием предыдущего слова). При поступлении слова номер состояния увеличивается на 4.

Рис. 4.19. Конечный автомат для реализации блока выборки команд

Чтобы функционировать правильно, схема выборки команд должна блокироваться в том случае, если от нее требуют произвести какие-то действия, которые она выполнить не может (например, передать значение в MBR2, когда в сдвиговом регистре находится только 1 байт, а память все еще занята вызовом нового слова). Кроме того, блок выборки команд не может выполнять несколько операций одновременно, поэтому вся поступающая информация должна передаваться последовательно. Наконец, всякий раз, когда изменяется значение PC, блок выборки команд должен обновляться. Все эти детали усложняют работу блока. Однако многие устройства разрабатываются в виде конечных автоматов.