нашего

сайта:

| Статус нашего сайта: |

|

ICQ Information Center |

ICQ SHOP ICQ SHOP5-значные 6-значные 7-значные 8-значные 9-значные Rippers List  ОПЛАТА ОПЛАТА СТАТЬИ СТАТЬИ СЕКРЕТЫ СЕКРЕТЫ HELP CENTER HELP CENTER OWNED LIST OWNED LIST РОЗЫСК!New! РОЗЫСК!New! ICQ РЕЛИЗЫ ICQ РЕЛИЗЫ Протоколы ICQ Протоколы ICQ LOL ;-) LOL ;-) Настройка компьютера Настройка компьютера Аватарки Аватарки Смайлики Смайлики СОФТ СОФТMail Checkers Bruteforces ICQTeam Soft 8thWonder Soft Other Progs ICQ Patches Miranda ICQ  ФорумАрхив! ФорумАрхив! ВАШ АККАУНТ ВАШ АККАУНТ

РекламаНаш канал:irc.icqinfo.ru |

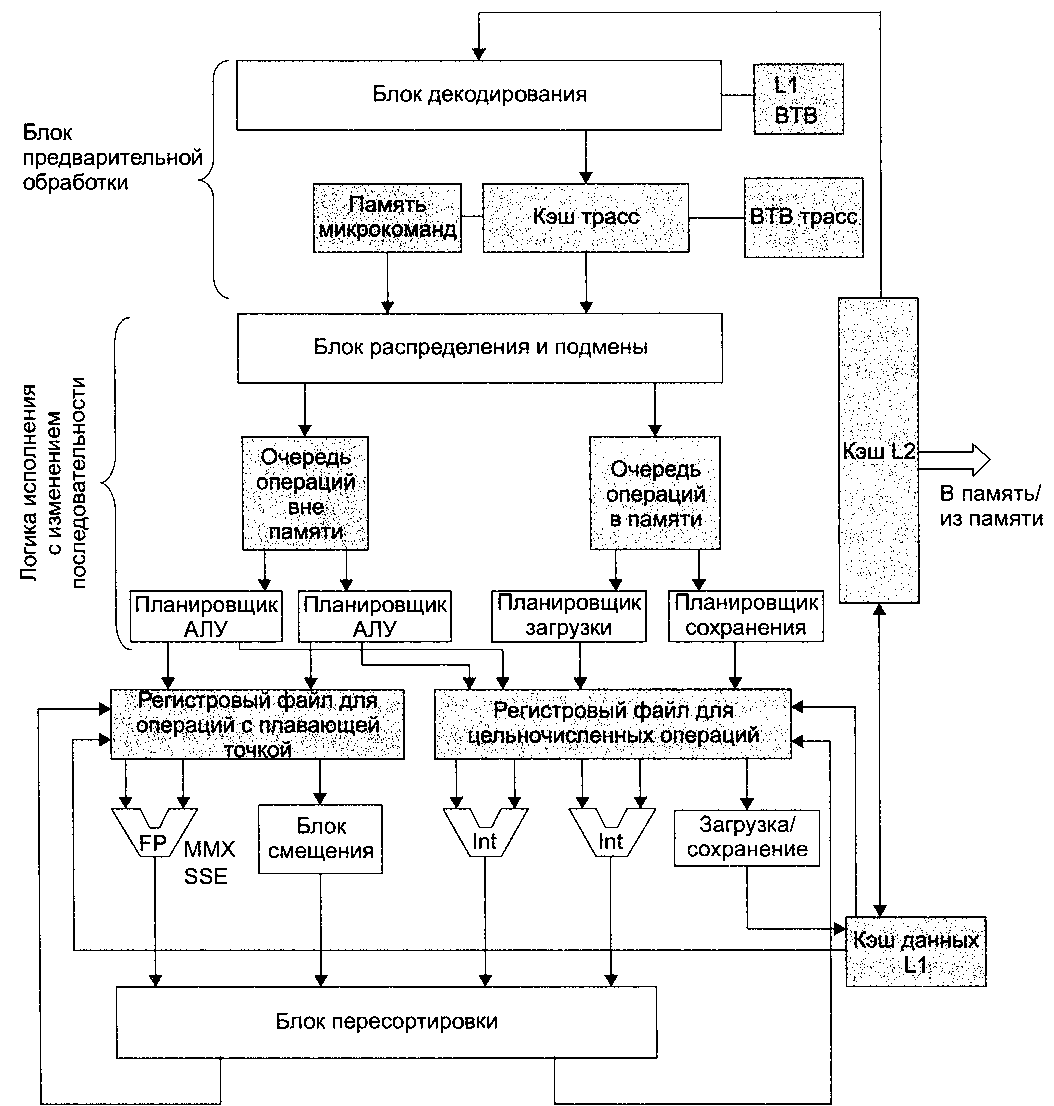

Таненбаум Э.- Архитектура компьютера. стр.248Декодированные микрооперации отправляются в кэш трасс (trace cache), в роли которого выступает кэш команд первого уровня. Поскольку кэшируются не исходные команды, а декодированные микрооперации, необходимость в повторном декодировании при извлечении команды из кэша трасс отпадает. В этом заключается одно из наиболее существенных расхождений между микроархитектурами NetBurst и Р6 (в последней команды Pentium удерживались в кэше команд первого уровня). Здесь же выполняется прогнозирование ветвлений. Команды передаются из кэша трасс планировщику команд в порядке, определяемом программой, но при их выполнении возможно отступление от этого порядка. При обнаружении микрооперации, которую нельзя выполнить, планировщик команд удерживает ее, одновременно продолжая обрабатывать поток команд — запускаются все последующие команды, которые не предусматривают обращение к занятым ресурсам (регистрам, функциональным блокам и т. д.). Здесь же выполняется подмена регистров, благодаря чему WAR- и WAW-взаи-мозависимые команды могут выполняться без задержки. Как уже отмечалось, очередность запуска команд может не соответствовать предусмотренной в программе. В то же время требование архитектуры Pentium, касающееся точных прерываний, говорит о том, что ISA-команды должны возвращать результаты без отступления от заданной программой последовательности. За реализацию этого требования отвечает блок пересортировки. В верхней правой части рисунка изображен блок исполнения, объединяющий специализированные блоки исполнения, которые непосредственно осуществляют целочисленные операции, операции с плавающей точкой и специализированные команды. Существует несколько блоков исполнения, работающих параллельно. Данные они получают из регистрового файла и кэша данных первого уровня. Конвейер NetBurst На рис. 4.32 приводится более подробная схема микроархитектуры NetBurst, в том числе ее конвейер. В верхней части схемы изображен блок предварительной обработки, ответственный за выборку команд из памяти и их подготовку к выполнению. Этот блок получает новые инструкции Pentium из кэша второго уровня порциями по 64 бит. Они декодируются в микрооперации и помещаются в кэш трасс. Емкость кэша трасс составляет 12 ООО микроопераций, и по своей производительности он сопоставим с традиционным кэшем первого уровня на 8 или 16 Кбайт.  Рис. 4.32. Упрощенная схема тракта данных Pentium 4 В кэше трасс каждые шесть микроопераций объединяются в группу, занимающую одну строку. Микрооперации из одной строки выполняются без нарушения последовательности, хотя они могут быть образованы из ISA-команд Pentium, отстоящих друг от друга на тысячи байтов. Для формирования более протяженных последовательностей микроопераций практикуется объединение трассируемых строк. Если для выполнения ISA-команды Pentium требуется более четырех микроопераций, она не декодируется и не помещается в кэш трасс. Вместо этого она снабжается специальным маркером, заставляющим систему провести поиск микроопераций в памяти микрокоманд. Таким образом, логика исполнения с изменением последовательности получает микрооперации путем извлечения из кэша трасс ранее декодированных ISA-команд или оперативного поиска сложных ISA-команд (например, команды смещения строки) в памяти микрокоманд. |