нашего

сайта:

| Статус нашего сайта: |

|

ICQ Information Center |

ICQ SHOP ICQ SHOP5-значные 6-значные 7-значные 8-значные 9-значные Rippers List  ОПЛАТА ОПЛАТА СТАТЬИ СТАТЬИ СЕКРЕТЫ СЕКРЕТЫ HELP CENTER HELP CENTER OWNED LIST OWNED LIST РОЗЫСК!New! РОЗЫСК!New! ICQ РЕЛИЗЫ ICQ РЕЛИЗЫ Протоколы ICQ Протоколы ICQ LOL ;-) LOL ;-) Настройка компьютера Настройка компьютера Аватарки Аватарки Смайлики Смайлики СОФТ СОФТMail Checkers Bruteforces ICQTeam Soft 8thWonder Soft Other Progs ICQ Patches Miranda ICQ  ФорумАрхив! ФорумАрхив! ВАШ АККАУНТ ВАШ АККАУНТ

РекламаНаш канал:irc.icqinfo.ru |

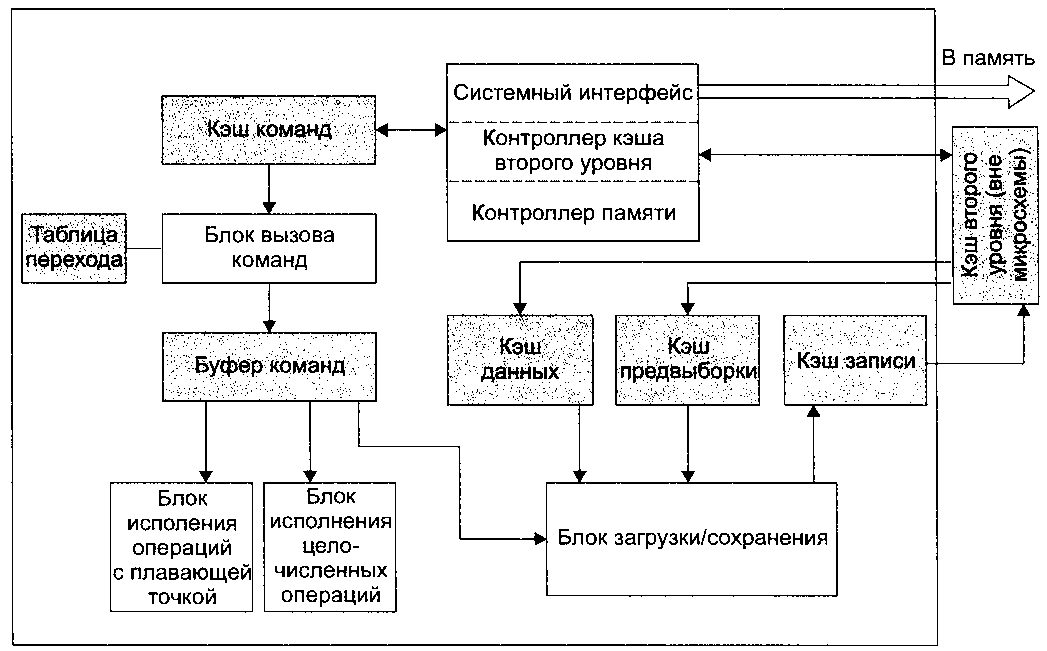

Таненбаум Э.- Архитектура компьютера. стр.252В отличие от Pentium 4, процессор UltraSPARC изначально проектировался как полноценная RISC-система. Следовательно, необходимости в сложном механизме преобразования старых CISC-команд в микрооперации в данном случае не было. Команды ядра представляют собой готовые микрооперации. Ситуация несколько осложняется появлением в последние годы новых команд обработки графических и мультимедийных данных, для выполнения которых требуются специальные устройства. Общий обзор системы UltraSPARC III Cu Структурная схема UltraSPARC III Си представлена на рис. 4.33. В целом, она значительно проще микроархитектуры NetBurst, применяемой в системах Pentium 4, что объясняется менее изощренной архитектурой системы команд UltraSPARC. Тем не менее по некоторым базовым компонентам сходство с Pentium 4 прослеживается. В первую очередь, это обусловлено технологическими и экономическими факторами. К примеру, в период проектирования этих микросхем объем кэшей данных первого составлял от 8 до 16 Кбайт. Этому стандарту соответствовали обе рассматриваемые микросхемы. Когда производство кэш-памяти первого уровня емкостью 64 Мбайт станет обоснованным с технологической и экономической точек зрения, все процессоры будут оснащаться уже новыми кэшами. Различия между Pentium 4 и UltraSPARC III Си связаны по большей части с тем, что в первом случае разработчикам пришлось обеспечить поддержку унаследованного набора CISC-команд, а во втором такой задачи не ставилось. В левой верхней части рис. 4.33 изображен 4-входовый ассоциативный кэш команд емкостью 32 Кбайт с 32-байтными строками. Поскольку большинство команд UltraSPARC занимают 4 байта, в этом кэше можно одновременно разместить около 8000 команд. По этому признаку UltraSPARC III Си несколько уступает кэшу трасс NetBurst. Блок вызова команд подготавливает для выполнения до четырех команд за цикл. В случае неудачного обращения в кэш-память первого уровня количество вызываемых команд уменьшается. При обнаружении условного перехода происходит обращение к таблице переходов емкостью 16 ООО записей; на основе ее содержания принимается решение о вызове следующей команды или команды, расположенной по целевому адресу. Повышать надежность прогнозирования ветвлений помогают дополнительные биты, связываемые с каждым словом в кэше команд. Подготовленные команды поступают в 16-командный буфер, который сглаживает направленный в конвейеры поток команд.  Рис. 4.33. Структурная схема процессора UltraSPARC III Си Как показано на рис. 4.33, из буфера команд команды попадают в блок исполнения целочисленных операций, блок исполнения операций с плавающей точкой и блок загрузки/сохранения. Блок исполнения целочисленных операций состоит из двух АЛУ и короткого конвейера для обработки команд перехода. Кроме того, здесь есть регистры ISA и временные регистры. Блок исполнения операций с плавающей точкой состоит из 32 регистров и трех независимых АЛУ, предназначенных для выполнения операций сложения/вычитания, умножения и деления, соответственно. Этот же блок выполняет графические операции. |