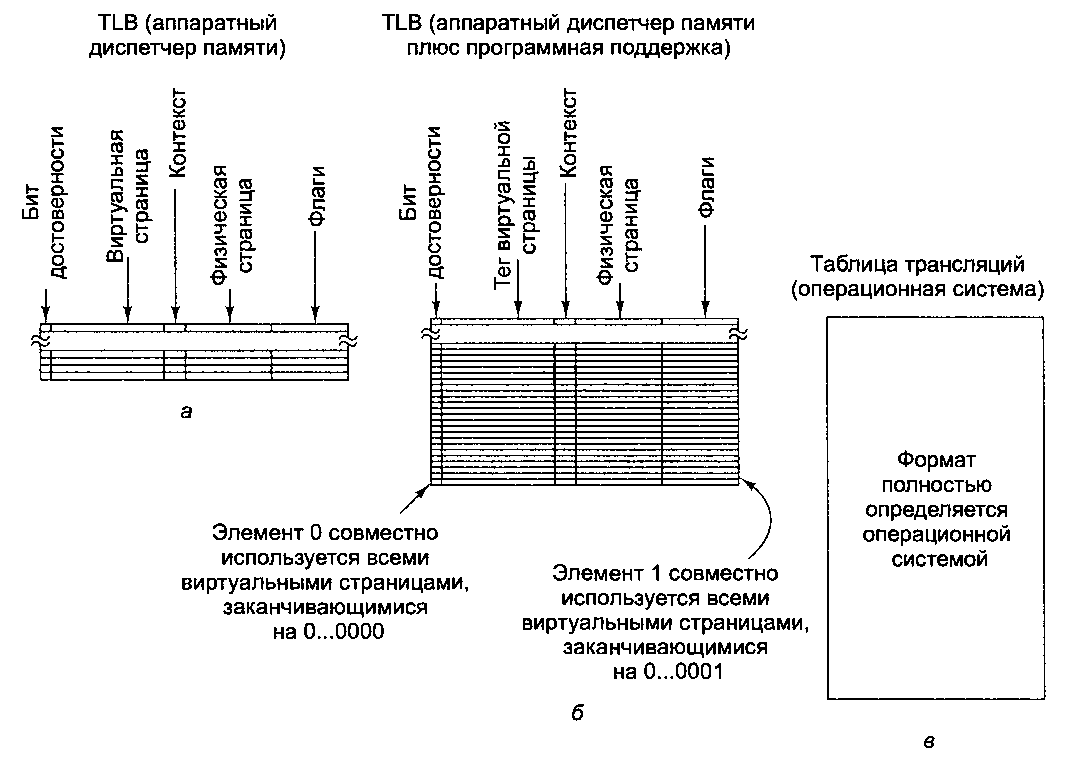

Рис. 6.16. Структуры данных, использующиеся для трансляции виртуального адреса в машине UltraSPARC III: буфер TLB (а); буфер TSB (б); таблица трансляции (в)

Операционная система сохраняет наиболее часто используемые элементы буфера TLB в так называемом буфере хранения преобразований (Translation Storage Buffer, TSB). Этот буфер построен как кэш-память прямого отображения виртуальных страниц. Каждый 16-байтный элемент буфера TSB указывает на одну виртуальную страницу pi содержит бит достоверности, номер контекста, тег виртуального адреса, номер физической страницы и несколько флаговых битов. Если размер кэш-памяти составляет, скажем, 8192 элемента, тогда все виртуальные страницы, у которых младшие 13 бит отображаются на 0000000000000, могут претендовать на элемент 0 в данной таблице. Точно так же все виртуальные страницы, у которых младшие биты отображаются на 0000000000001, претендуют на элемент 1 в этой таблице, как показано на рис. 6.16, б. Размер таблицы определяется программно и передается диспетчеру памяти через специальные регистры, доступные только для операционной системы.

При TLB-промахе операционная система проверяет, нет ли нужной виртуальной страницы в соответствующем элементе буфера TSB. Диспетчер памяти вычисляет адрес этого элемента и помещает его в свой внутренний регистр, доступный для операционной системы. Если нужный элемент в буфере TSB есть, то один из элементов удаляется из буфера TLB и на его место копируется элемент из буфера буфере TSB. То, какой элемент нужно выкинуть, определяется аппа-ратно с помощью алгоритма LRU.

Если нужной виртуальной страницы не обнаруживается, операционная система ищет информацию о странице в таблице трансляции. Поскольку здесь аппаратное обеспечение в поиске элементов не участвует, операционная система может использовать любой формат. Например, она может хэшировать номер виртуальной страницы, разделив его на какое-либо число р, и использовать остаток для индексирования таблицы указателей, каждый из которых указывает на связанный список виртуальных страниц, разделенных на р. Отметим, что эти элементы — не собственно страницы, а элементы буфера TSB. Если поиск страницы в таблице трансляции привел к нахождению нужной страницы в памяти, то элемент TSB в кэш-памяти обновляется. Если в результате поиска обнаружилось, что нужной страницы нет в памяти, происходит стандартная ошибка отсутствия страницы.

Сравним схемы разбиения на страницы Pentium 4 и UltraSPARC HI. Pentium 4 поддерживает «чистую» сегментацию, «чистое» разбиение на страницы и сегментацию в сочетании с разбиением на страницы. UltraSPARC II поддерживает только разбиение на страницы. Pentium 4 в случае TLB-промаха перезагружает элемент буфера TLB аппаратно. UltraSPARC III в случае TLB-промаха просто передает управление операционной системе.

Причина этого отличия состоит в том, что в Pentium 4 32-разрядные сегменты, а такие маленькие сегменты (только 1 млн страниц) могут обрабатываться лишь с помощью таблиц страниц. Теоретически у Pentium 4 могли бы возникнуть проблемы, если бы программа использовала тысячи сегментов, но так как ни одна из версий Windows или UNIX не поддерживает более одного сегмента на процесс, никаких проблем не возникает. UltraSPARC III — 64-разрядная машина. Она может содержать до 2 млрд страниц, поэтому механизм таблиц страниц не работает. В будущем все машины будут иметь 64-разрядные виртуальные адресные пространства, и схема UltraSPARC III станет нормой.