нашего

сайта:

| Статус нашего сайта: |

|

ICQ Information Center |

ICQ SHOP ICQ SHOP5-значные 6-значные 7-значные 8-значные 9-значные Rippers List  ОПЛАТА ОПЛАТА СТАТЬИ СТАТЬИ СЕКРЕТЫ СЕКРЕТЫ HELP CENTER HELP CENTER OWNED LIST OWNED LIST РОЗЫСК!New! РОЗЫСК!New! ICQ РЕЛИЗЫ ICQ РЕЛИЗЫ Протоколы ICQ Протоколы ICQ LOL ;-) LOL ;-) Настройка компьютера Настройка компьютера Аватарки Аватарки Смайлики Смайлики СОФТ СОФТMail Checkers Bruteforces ICQTeam Soft 8thWonder Soft Other Progs ICQ Patches Miranda ICQ  ФорумАрхив! ФорумАрхив! ВАШ АККАУНТ ВАШ АККАУНТ

РекламаНаш канал:irc.icqinfo.ru |

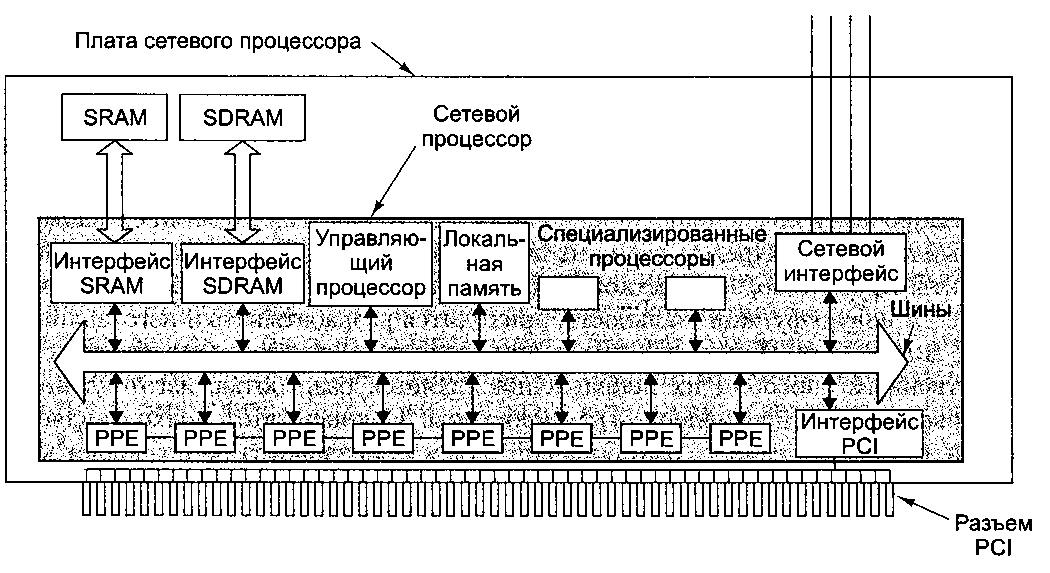

Таненбаум Э.- Архитектура компьютера. стр.443Обычно на плате имеется как статическая (SRAM), так и синхронная динамическая оперативная память (SDRAM) — эти виды памяти применяются для разных целей. SRAM быстрее SDRAM, но из-за дороговизны памяти этого типа обычно немного. Она используется для хранения таблиц маршрутизации и прочих ключевых структур данных, в то время как в SDRAM записываются сами обрабатываемые пакеты. Благодаря тому, что память обоих этих типов располагается вне кристалла сетевого процессора, можно гибко подойти к вопросу о выборе объема памяти. Так, в простых системах с единственной сетевой линией (такие платы могут ставиться, например, в персональный компьютер или сервер) памяти может быть немного, в то время как маршрутизатору ее требуется намного больше.  Рис. 8.13. Кристалл и плата типичного сетевого процессора Сетевые процессоры оптимизированы для быстрой обработки большого количества входящих и исходящих пакетов. Это означает, что по каждой из сетевых линий проходят миллионы пакетов в секунду, а маршрутизатор должен поддерживать десятки таких линий. Столь серьезных показателей можно достигнуть только на процессорах с высокой степенью внутреннего параллелизма. Кроме того, в процессор обязательно входят несколько РРЕ-контроллеров (Protocol/ Programmable/Packet Processing Engine — программируемая система обработки пакетов и протоколов), каждая из которых состоит из RISC-ядра (возможно, модифицированного) и внутренней памяти небольшого объема для хранения программы и нескольких переменных. Есть два подхода к организации РРЕ-контроллеров. В простейшем случае все РРЕ-контроллеры делаются идентичными. Когда в сетевой процессор приходит новый пакет, он передается для обработки тому РРЕ-контроллеру, который в данный момент бездействует. Если свободных РРЕ-контроллеров нет, пакет ставится в очередь в расположенной на плате памяти SDRAM, ожидая освобождения одного из РРЕ-контроллеров. При такой организации горизонтальные связи, показанные на рис. 8.13, отсутствуют, так как у разных РРЕ-контроллеров нет необходимости общаться друг с другом. Другой подход к организации РРЕ-контроллеров — конвейер, где каждый из РРЕ-контроллеров выполняет один этап обработки, после чего передает указатель на полученный пакет следующему РРЕ-контроллеру в конвейере. Такой конвейер работает во многом аналогично конвейерам ЦП, которые рассматривались в главе 2. В обоих вариантах организации РРЕ-контроллеры являются полностью программируемыми. В более совершенных сетевых процессорах РРЕ-контроллеры поддерживают многопоточность, то есть каждый из них имеет несколько наборов регистров и аппаратный регистр, показывающий, какой из наборов используется. Это позволяет одновременно выполнять несколько программ (то есть программных потоков) и переключаться между ними, просто изменяя переменную «текущего рабочего набора регистров». Когда один из программных потоков вынужден ждать (например, при обращении к SDRAM, на которое требуется несколько циклов), РРЕ-контроллер может быть мгновенно переключен на поток, способный продолжать работу. Это позволяет добиваться высокой загрузки РРЕ-контроллеров, даже несмотря на необходимость часто ожидать завершения обмена данными с SDRAM или других медленных внешних операций. |