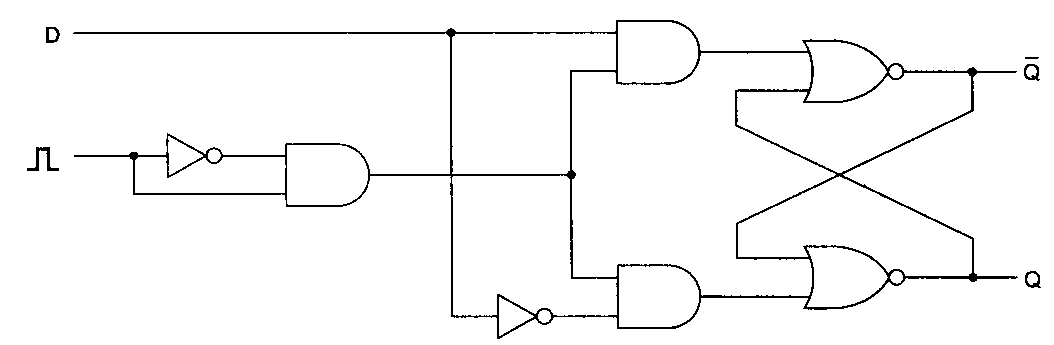

Рис. 3.25. D-триггер

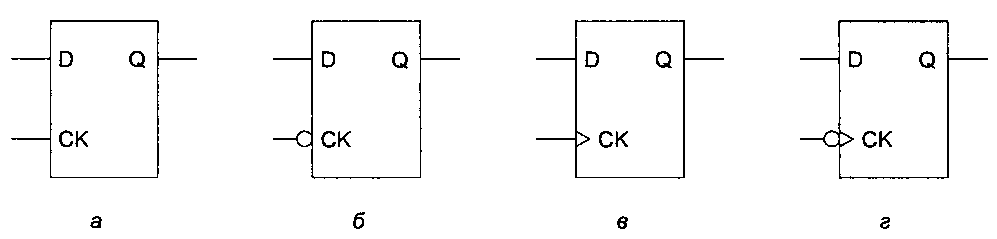

Стандартные обозначения защелок и триггеров показаны на рис. 3.26. На рис. 3.26, а изображена защелка, состояние которой загружается тогда, когда синхронизирующий сигнал СК (от слова clock) равен 1, в противоположность защелке, изображенной на рис. 3.26, б, у которой синхронизирующий сигнал обычно равен 1, но переходит на 0, чтобы загрузить состояние из линии D. На рис. 3.26, в и г изображены триггеры. О том, что это триггеры, а не защелки, говорит уголок на синхронизирующем входе. Триггер на рис. 3.26, в изменяет состояние на фронте синхронизирующего импульса (переход от 0 к 1), тогда как триггер на рис. 3.26, г изменяет состояние на спаде (переход от 0 к 1). Многие (хотя не все) защелки и триггеры также имеют выход Q, а у некоторых есть два дополнительных входа: Set (установка) или Preset (предварительная установка) и Reset (сброс) или Clear (очистка). Первый вход (Set или Preset) устанавливает Q = 1, а второй (Reset или Clear) — Q = 0.

Рис. 3.26. D-защелки и D-триггеры

Регистры

Существуют различные конфигурации триггеров. На рис. 3.27, а изображена схема, содержащая два независимых Б-триггера с сигналами предварительной установки и очистки. Хотя эти два триггера находятся на одной микросхеме с 14 выводами, они не связаны между собой. Совершенно по-другому устроен «восьмикратный» триггер, изображенный на рис. 3.27, б. Здесь, в отличие от предыдущей схемы, у восьми триггеров нет выхода (2 и линий предварительной установки, а все синхронизирующие линии связаны вместе и управляются выводом 11. Сами триггеры того же типа, что и на рис. 3.26, г, но инвертирующие входы аннулируются инвертором, связанным с выводом 11, поэтому триггеры запускаются при переходе от 0 к 1. Все восемь сигналов очистки тоже объединены, поэтому когда вывод 1 переходит в состояние 0, все триггеры переходят в состояние 0. Если вам не понятно, почему вывод 11 инвертируется на входе, а затем инвертируется снова при каждом сигнале С К, то ответ прост: входной сигнал не имеет достаточной мощности, чтобы запустить все восемь триггеров; входной инвертор на самом деле используется в качестве усилителя.

Одна из причин объединения линий синхронизации и линий очистки в микросхеме на рис. 3.27, б — экономия выводов. В то же время микросхема данной конфигурации несколько отличается от восьми не связанных между собой триггеров и используется в качестве одного 8-разрядного регистра. Две такие микросхемы могут работать параллельно, образуя 16-разрядный регистр. Для этого нужно связать соответствующие выводы 1 и И. Регистры и их применение мы рассмотрим более подробно в главе 4.

Организация памяти

Хотя мы и совершили переход от простой памяти емкостью 1 бит (см. рис. 3.23) к 8-разрядной памяти (см. рис. 3.27, б), чтобы построить память большого объема, требуется другой способ организации, при котором можно обращаться к отдельным словам. Пример организации памяти, которая удовлетворяет этому критерию, показан на рис. 3.28. Эта память содержит четыре 3-разрядных слова. Каждая операция считывает или записывает целое 3-разрядное слово. Хотя общий объем памяти (12 бит) не намного больше, чем у 8-разрядного триггера, та кая память требует меньшего количества выводов и, что особенно важно, подобная организация применима для построения памяти большого объема.