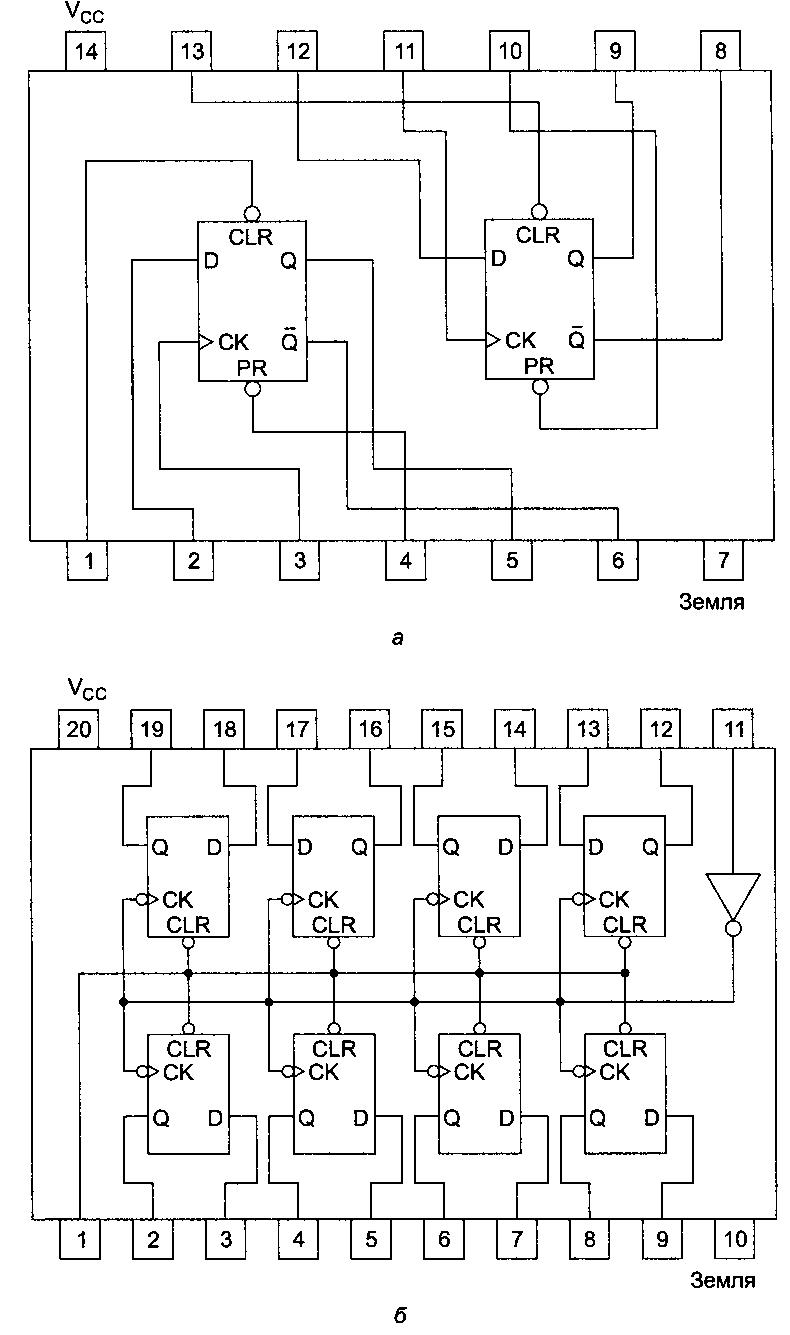

Рис. 3.27. Сдвоенный Р-триггер (а), «восьмикратный» триггер (б)

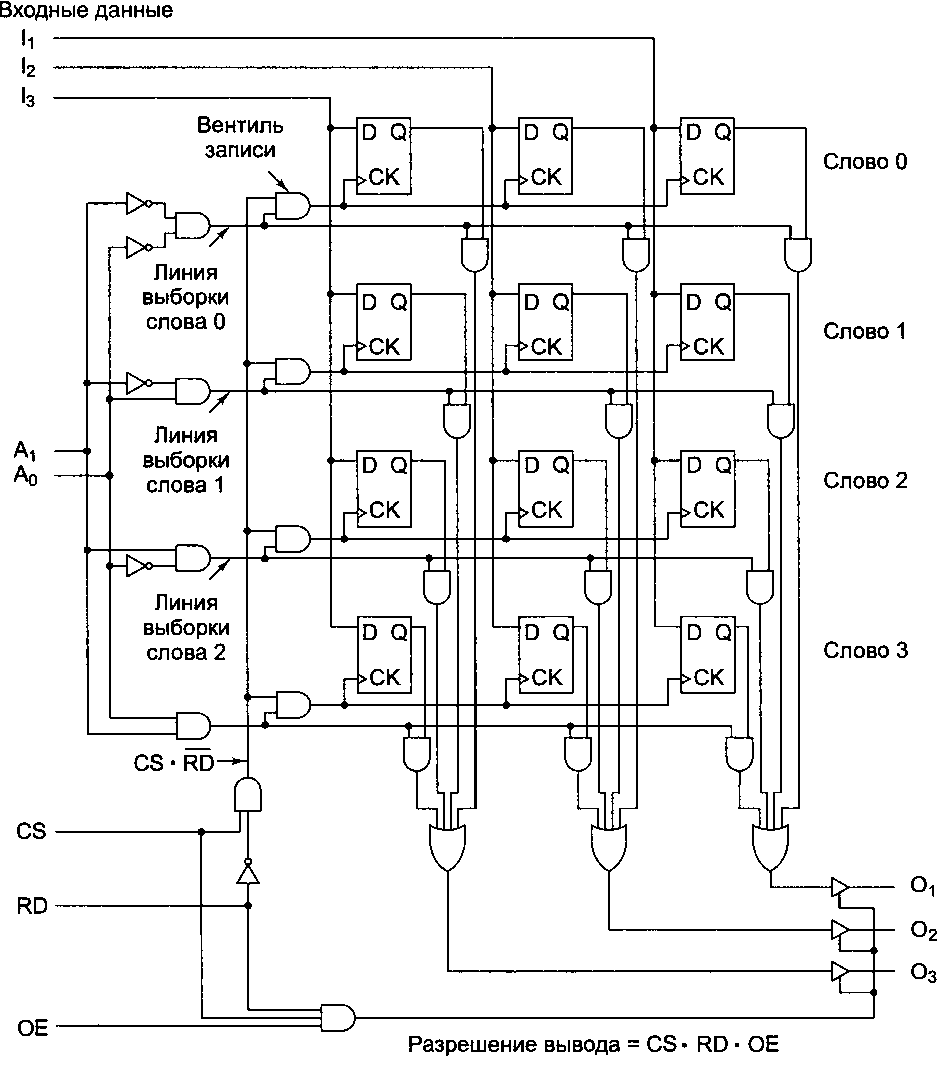

Рис. 3.28. Логическая блок-схема для памяти 4x3. Каждый ряд представляет одно из 3-разрядных слов. При считывании и записи всегда считывается или записывается целое слово

Хотя организация памяти, изображенной на рис. 3.28, может на первый взгляд показаться сложной, на самом деле она очень проста благодаря своей регулярной структуре. Микросхема содержит 8 входных линий, в частности 3 входа для данных — I0, Ii и 12; 2 входа для адресов — А0 и At; 3 входа для управления — CS (Chip Select — выбор элемента памяти), RD (ReaD — чтение, этот сигнал позволяет отличать считывание от записи) и ОЕ (Output Enable — разрешение выдачи выходных сигналов), а также 3 выходные линии для данных — О0, и 02. Такую память в принципе можно поместить в корпус с 14 выводами (включая питание и землю), а 8-разрядный триггер требует наличия 20 выводов.

Чтобы выбрать микросхему памяти, внешняя логика должна установить сигнал С8 в 1, а также установить сигнал 1Ш в 1 для чтения и в 0 для записи. Две адресные линии должны указывать, какое из четырех 3-разрядных слов нужно считывать или записывать. При считывании входные линии для данных не используются. Выбирается слово и помещается на выходные линии для данных. При записи биты, находящиеся на входных линиях для данных, загружаются в выбранное слово памяти; выходные линии при этом не используются.

А теперь давайте посмотрим, как работает память, изображенная на рис. 3.28. Четыре вентиля И для выбора слов в левой части схемы формируют декодер. Входные инверторы расположены так, что каждый вентиль запускается определенным адресом. Каждый вентиль приводит в действие линию выбора слов (для слов 0, 1, 2 и 3). Когда микросхема должна производить запись, вертикальная линия С8-1Ш получает значение 1, запуская один из четырех вентилей записи. Выбор вентиля зависит от того, какая именно линия выбора слов равна 1. Выходной сигнал вентиля записи приводит в действие все сигналы СК для выбранного слова, загружая входные данные в триггеры для этого слова. Запись производится только в том случае, если сигнал С8 равен 1, а 1Ш — 0, при этом записывается только слово, выбранное адресами Ао и А^ остальные слова не меняются.

Процесс считывания сходен с процессом записи. Декодирование адреса происходит точно так же, как и при записи. Но в данном случае линия С8-1Ш принимает значение 0, поэтому все вентили записи блокируются, и ни один из триггеров не меняется. Вместо этого линия выбора слов запускает вентили И, связанные с битами £) выбранного слова. Таким образом, выбранное слово передает свои данные в 4-входовые вентили ИЛИ, расположенные в нижней части схемы, а остальные три слова выдают 0. Следовательно, выход вентилей ИЛИ идентичен значению, сохраненному в данном слове. Остальные три слова никак не влияют на выходные данные.

Мы могли бы разработать схему, в которой три вентиля ИЛИ соединялись бы с тремя линиями вывода данных, но это вызвало бы некоторые проблемы. Мы рассматривали линии ввода данных и линии вывода данных как разные линии. На практике же используются одни и те же линии. Если бы мы связали вентили ИЛИ с линиями вывода данных, микросхема пыталась бы выводить данные (то есть задавать каждой линии определенную величину) даже в процессе записи, мешая нормальному вводу данных. По этой причине желательно каким-то образом соединять вентили ИЛИ с линиями вывода данных при считывании и полностью разъединять их при записи. Все, что нам нужно, — электронный переключатель, который может устанавливать и разрывать связь за несколько наносекунд.