В состав одной TriMedia-команды может входить до пяти операций. В полностью оптимальных условиях за тактовый цикл запускается одна команда и выбирается пять операций. Номинальная тактовая частота процессора составляет 266 или 366 МГц, но так как за один цикл может выполняться до пяти операций, фактическое быстродействие в пять раз больше. При дальнейшем изложении мы будем исходить из характеристик реализации ТМ3260 процессора. Другие версии TriMedia имеют ряд малозначительных отличий.

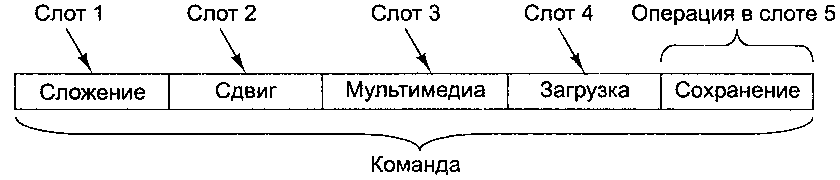

Стандартная TriMedia-команда изображена на рис. 8.3. По своему характеру команды варьируются от общераспространенных 8-, 16- и 32-разрядных целочисленных команд до команд с плавающей точкой стандарта IEEE 754 и команд параллельной обработки мультимедиа. Исполнение пяти операций за цикл и наличие команд параллельной обработки мультимедийных данных позволяют процессору TriMedia программно декодировать потоковое цифровое видео, поступающее с видеокамеры, сохраняя исходные размер и частоту кадров.

Рис. 8.3. Стандартная ТпМесНа-команда с пятью операциями

В ТпМесИа используется память с байтовой организацией, а регистры ввода-вывода отображаются на пространство памяти. Полуслова (16 бит) и полные слова (32 бит) выравниваются по естественным границам. Порядок следования байтов может быть как прямым, так и обратным — в зависимости от бита слова состояния программы, выставляемого операционной системой. Этот бит определяет механизм передачи данных операций загрузки и сохранения между памятью и регистрами. В процессоре предусмотрена разделенная 8-входовая ассоциативная кэш-память с одинаковой длиной строки (64 байт) в кэшах команд и данных. Емкость кэша команд составляет 64 Кбайт; емкость кэша данных — 16 Кбайт.

Существует 128 универсальных 32-разрядных регистров. Значения регистров 110 и Ш равны аппаратным нулю и единице, соответственно. Остальные 126 регистров функционально эквивалентны и могут применяться для любых целей. Кроме того, предусмотрены четыре специализированных 32-разрядных регистра:

счетчик команд, регистр слова состояния программы и два регистра, связанные с прерываниями. Наконец, один 64-разрядный регистр подсчитывает число циклов процессора с момента последнего сброса. При тактовой частоте 300 МГц полный цикл счетчика составляет 2000 лет.

В процессоре ТМ3260 есть 11 функциональных блоков, предназначенных для выполнения арифметических, логических и управляющих операций (также есть блок управления кэшем, но его мы рассматривать не будем). Все они перечислены в табл. 8.1. В первых двух столбцах приводятся имя блока и краткое описание выполняемых им функций. В третьем столбце указывается число аппаратных копий блока. Четвертый столбец содержит значение ожидания (точнее, число циклов) до завершения операции. В этом контексте нелишне отметить, что все функциональные блоки, за исключением блока извлечения квадратного корня и деления чисел с плавающей точкой, конвейеризированы. Хотя ожидание говорит о том, сколько нужно ждать до завершения операции, не следует забывать, что в каждом новом цикле можно начинать новые операции. Так, в каждой из трех последовательных команд может содержаться по две операции загрузки, а значит, одновременно на разных этапах исполнения может находиться шесть операций загрузки.