Схема суперскалярного процессора приведена на рис. 2.5. В наиболее распространенных конфигурациях команда должна быть готова к исполнению в определенной точке конвейера. Суперскалярные процессоры способны за один тактовый цикл вызывать несколько команд. Число фактически вызываемых команд зависит как от конструкции процессора, так и от текущей ситуации. Аппаратные ограничения диктуют максимальное число одновременно вызываемых команд — обычно от двух до шести. К тому же, если для выполнения команды нужен недоступный функциональный блок или еще не полученный результат выполнения другой команды, такая команда не будет вызвана даже при наличии физической возможности.

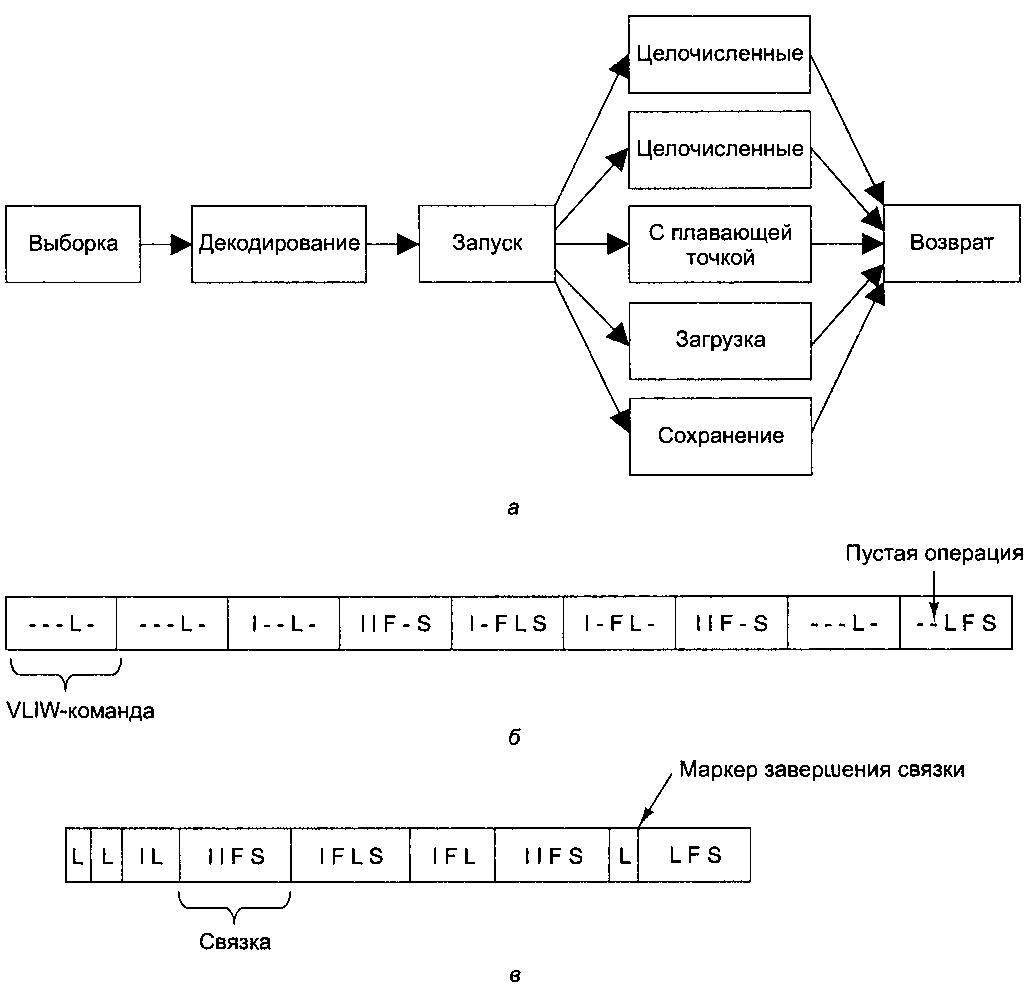

Другой вид параллелизма на уровне команд реализуется в процессорах со сверхдлинным командным словом (Very Long Instruction Word, VLIW). В своем первоначальном исполнении VLIW-системы, действительно, отличались длинными словами с командами, обращавшимися к нескольким функциональным блокам. Для примера рассмотрим конвейер, изображенный на рис. 8.2, а. Он включает в себя пять функциональных блоков и способен одновременно выполнять две целочисленные операции, одну операцию с плавающей точкой, одну команду загрузки и одну команду сохранения. В одной команде этой VLIW-системы содержится пять кодов операций и пять пар операндов — по одному коду и одной паре на каждый функциональный блок. С учетом того, что код операции занимает 6 бит, регистр — 5 бит, а ячейка памяти — 32 бита, общая длина команды может достигать 134 бита, что, согласитесь, немало.

Однако такое решение было признано неудачным. Дело в том, что не все команды могли обращаться к соответствующим функциональным блокам, в результате в изобилии появлялись бессмысленные пустые операции (рис. 8.2, б). В современных VLIW-системах должен быть предусмотрен какой-либо механизм маркировки связок команд, например, для этого может использоваться бит «завершения связки» (рис. 8.2, в). Процессор может выбрать и запустить связку целиком. Задача по подготовке связок команд, которые могут выполняться совместно, решается компилятором.

Рис. 8.2. Конвейер процессора (а); последовательность \/1_1\М-команд (б); поток команд

с отмеченными связками (е)

Фактически в VLIW-системах решение проблемы совместимости команд переносится с периода исполнения на стадию компиляции. В результате аппаратное обеспечение упрощается и удешевляется. Кроме того, поскольку в работе компилятора нет жестких временных ограничений, связки команд формируются более осмысленно, нежели если бы это происходило в период исполнения. К сожалению, ввести в практику столь радикальные преобразования архитектуры процессора очень сложно, что подтверждается более чем умеренными темпами распространения процессора Itanium.

Нелишне заметить, что параллелизм на уровне команд не является единственно возможной формой низкоуровневого параллелизма. Существует также параллелизм на уровне памяти, предусматривающий одновременное исполнение в памяти множества операций [42].

VLIW-процессор TriMedia

В главе 5 на примере процессора Itanium 2 мы уже сталкивались с архитектурой VLIW. Теперь познакомимся с другим VLIW-процессором — TriMedia производства компании Philips. TriMedia — это встроенный процессор для устройств обработки изображений, а также аудио- и видеустройств, таких как CD-, DVD-и МРЗ-плееры, устройства записи CD и DVD, интерактивные телевизоры, цифровые фотокамеры, видеокамеры и т. д. Учитывая специализацию, нет ничего удивительного в многочисленных отличиях TriMedia от Itanium 2 — универсального процессора для высокопроизводительных серверов.