нашего

сайта:

| Статус нашего сайта: |

|

ICQ Information Center |

ICQ SHOP ICQ SHOP5-значные 6-значные 7-значные 8-значные 9-значные Rippers List  ОПЛАТА ОПЛАТА СТАТЬИ СТАТЬИ СЕКРЕТЫ СЕКРЕТЫ HELP CENTER HELP CENTER OWNED LIST OWNED LIST РОЗЫСК!New! РОЗЫСК!New! ICQ РЕЛИЗЫ ICQ РЕЛИЗЫ Протоколы ICQ Протоколы ICQ LOL ;-) LOL ;-) Настройка компьютера Настройка компьютера Аватарки Аватарки Смайлики Смайлики СОФТ СОФТMail Checkers Bruteforces ICQTeam Soft 8thWonder Soft Other Progs ICQ Patches Miranda ICQ  ФорумАрхив! ФорумАрхив! ВАШ АККАУНТ ВАШ АККАУНТ

РекламаНаш канал:irc.icqinfo.ru |

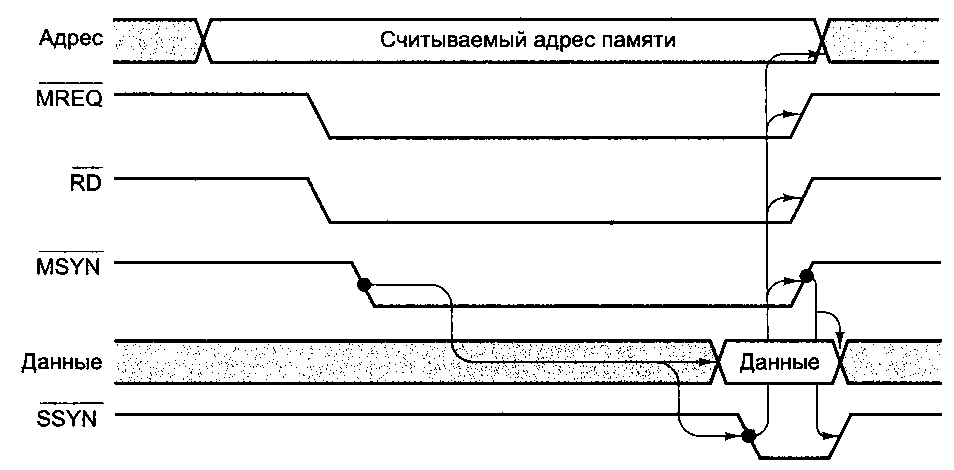

Таненбаум Э.- Архитектура компьютера. стр.149Интервалы Тмн и TRH определяют, сколько времени требуется на отмену сигналов MREQ и RD после того, как данные стробированы. Наконец, интервал TDH определяет, сколько времени память должна держать данные на шине после снятия сигнала RD. В нашем примере при данном процессоре память может удалить данные с шины, как только сбрасывается сигнал RD; в случае других процессоров данные могут сохраняться еще некоторое время. Необходимо подчеркнуть, что наш пример представляет собой весьма упрощенную версию реальных временных ограничений. В действительности таких ограничений гораздо больше. Тем не менее этот пример наглядно демонстрирует, как работает синхронная шина. Отметим, что сигналы управления могут задаваться низким или высоким напряжением. Что является более удобным в каждом конкретном случае, должен решать разработчик, хотя, по существу, выбор произволен. Такую свободу выбора можно назвать «аппаратным» аналогом ситуации, при которой программист может представить свободные дисковые блоки в битовом отображении как в виде нулей, так и в виде единиц. Асинхронные шины Хотя использовать синхронные шины благодаря дискретным временным интервалам достаточно удобно, здесь все же есть некоторые проблемы. Например, если процессор и память способны закончить передачу за 3,1 цикла, они вынуждены продлить ее до 4,0 циклов, поскольку неполные циклы запрещены. Еще хуже то, что если однажды был выбран определенный цикл шины и в соответствии с ним разработана память и карты ввода-вывода, то в будущем трудно делать технологические усовершенствования. Например, предположим, что через несколько лет после выпуска системы, изображенной на рис. 3.35, появилась новая память с временем доступа не 15, а 8 не. Это время позволяет избавиться от периода ожидания и увеличить скорость работы машины. А теперь представим, что появилась память с временем доступа 4 не. При этом улучшения производительности уже не будет, поскольку в данной разработке минимальное время чтения — 2 цикла. Если синхронная шина соединяет ряд устройств, одни из которых работают быстро, а другие — медленно, шина подстраивается под самое медленное устройство, а более быстрые не могут использовать свой потенциал полностью. По этой причине были разработаны асинхронные шины, то есть шины без задающего генератора (рис. 3.36). Здесь ничего не привязывается к генератору. Когда задающее устройство устанавливает адрес, сигнал MREQ, RD или любой другой требуемый сигнал, оно выдает специальный синхронизирующий сигнал MSYN (Master SYNchronization). Когда подчиненное устройство получает этот сигнал, оно начинает выполнять свою работу настолько быстро, насколько это возможно. Когда работа заканчивается, подчиненное устройство выдает сигнал SSYN (Slave SYNchronization).  Рис. 3.36. Работа асинхронной шины Сигнал ББУЫ означает для задающего устройства, что данные доступны. Оно фиксирует их, а затем сбрасывает адресные линии вместе с сигналами М11Е(), КБ и МЗУЫ. Сброс сигнала МБУЫ означает для подчиненного устройства, что цикл закончен, поэтому устройство сбрасывает сигнал Б БУКТ, и все возвращается к первоначальному состоянию, когда все сигналы сброшены. |